STM32 SystemClock Modified When Debugging with OpenOCD

Phenomenon

The chip is STM32F4( and it’s doesn’t matter from the view in the end, while the number of code line may vary)

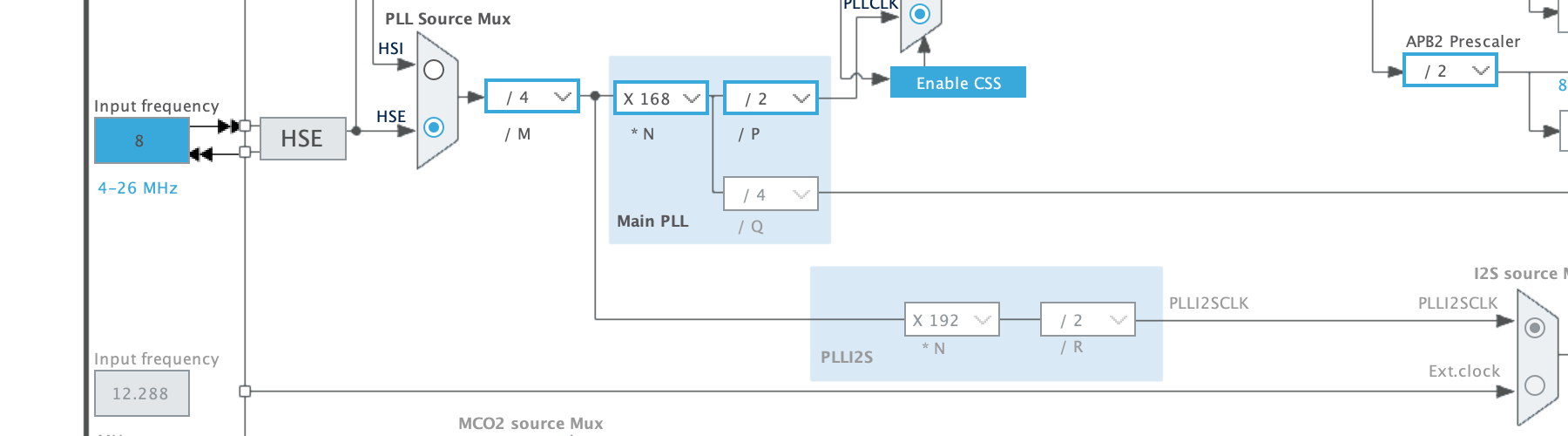

When enabling PLL in Clock Configuration in CubeMX, no matter how low or high the SYSCLK or HCLK is, it would stuck at SystemClock_Config();

Specifically, it stuck when configuring RCC and PLL

1 | //Line 149 in main.c |

Suspicion

System’s clock is too high

The official highest clock speed for STM32F4 is 168 MHz and the HSI and HSE is 16 MHz and 8MHz.

Something strange happens:

- Decreasing the clock to 72MHz doesn’t help at all. Which excludes the overclock speed.

- If the system clock comes directly from HSI or HSE, the problem dismisses.

- The system works fine in this circumstance, however, 16MHz or 8MHz is too slow for application.

- Even HSI encounters the problem, the failure of HSE or the wrong layout could be excluded.

- If the PLL is participated, no matter how low the clock speed is, or whether the clock source comes from HSI or HSE, the problem is always encountered

After that, I tried to use the examples provided by manufacturer, which is also weird:

- The source code of RCC/PLL is pretty much similar to generated before, while none of them could work

- The binary program provided could work perfectly! Which excludes the problems from hardware.

After some tries, the problem is narrowed down to the RCC/PLL configuration

CubeMX and ST’s bug

Though I have generated code thousands times directly from CubeMX and it ran perfectly before on STM32F103, it could be possible a vital bug made by ST official. And it could be true. Some reported a bug of mis-configuring a register in HAL few years ago and ST promised to solve the problem by updating a firmware pack.

https://community.st.com/t5/stm32-mcus-embedded-software/bugs-encountered-in-f4-rcc-hal-code-are-there-any-workarounds/td-p/209967

Sadly, I am at the latest version of firmware and the bug should be fixed. I even tried to retreat to the previous version, it still can’s solve the problem.

Debugger’s fault

Debugger comes to my mind because of a coincidence that flashing the firmware without debug could dismiss the problem. I have to say I was in a trap at the very beginning of solving this problem: the first time I encountered it is because I want to grab the raw data with debug mode from a serial receiving code. The blink code works fine when flashing directly.

OK, the problem is narrowed down to the debugger, ST-Link.

Reasons

I was inspired by https://www.eevblog.com/forum/microcontrollers/stm32-clock-gets-modified-when-debugger-is-connected/

OpenOCD modifies register when triggering reset-init

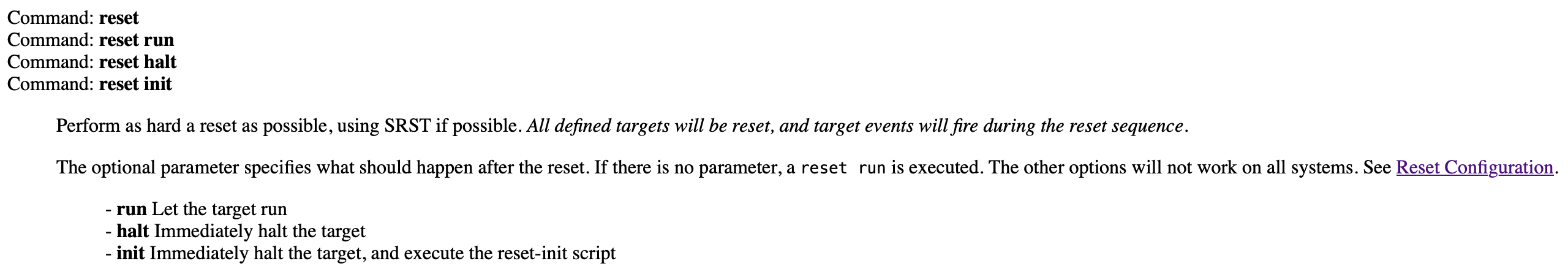

There are 3types of reset by OpenOCD:

When reset init is triggered, the code from stm32f4x.cfg below would be executed:

1 | $_TARGETNAME configure -event reset-init { |

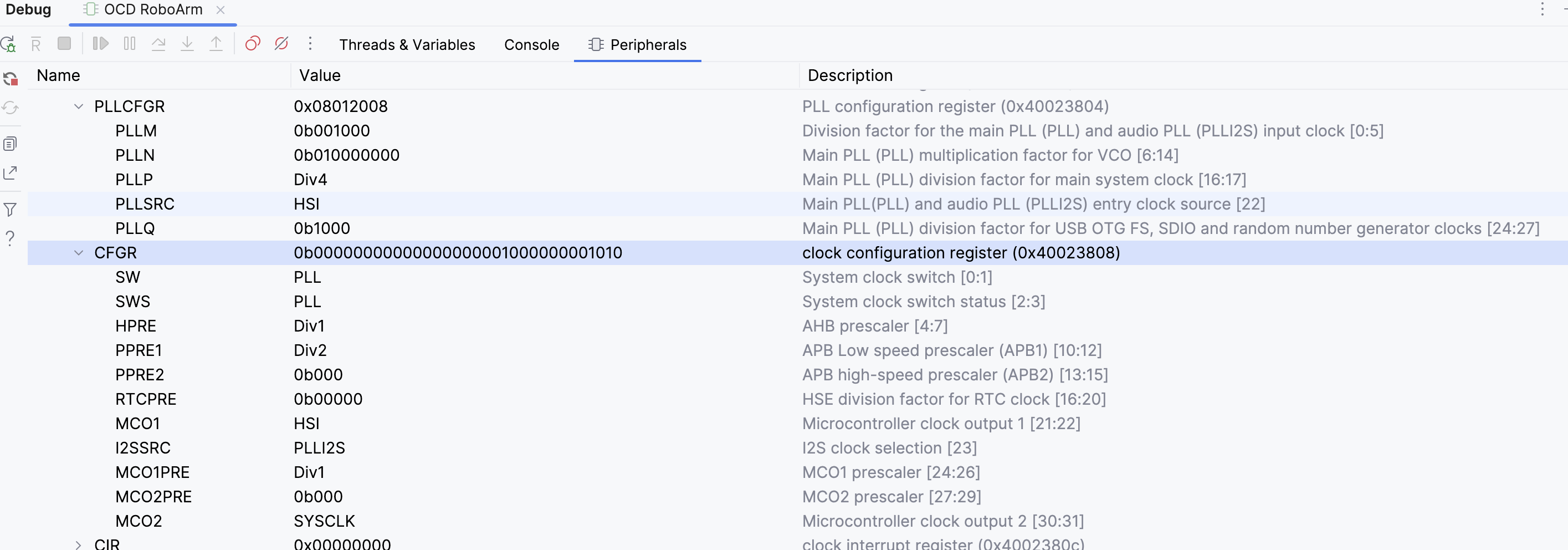

It’s obvious that RCC and PLL is configured to 64MHz instead of 16MHz from HSI by default. It’s considered that OpenOCD needs to initialize the flash controller in order to program the memory.

After that, there is no more process of reset and the data in register remains.

Solution

- Use

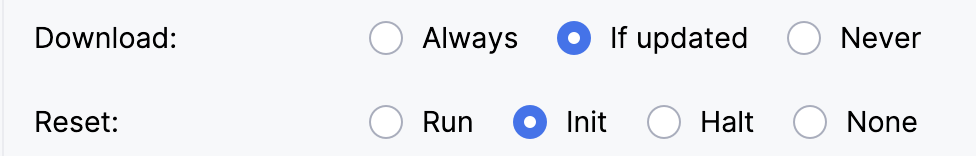

reset haltinstead ofreset initfor debug

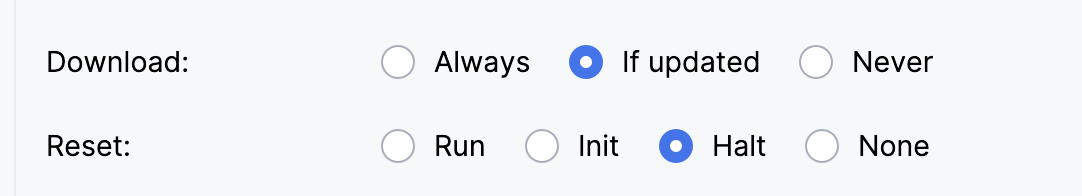

The operation is pretty simple, change the option in CLion from:

to:

Besides

It’s hard to believe the problem stuck me for 2 days only requires a click.

It’s my first time loading peropherals svd in CLion for debug. It saves a lot of effort comparing to referring data sheet.

Here’s a repo with all svd file for STM32